Welcome back for the second half of this month's sensible semiconductor news update! In this installment, we’ll dive into the next generation of memory and processing technologies, from the super-flexible CXL-attached memory to tomorrow’s energy-efficient ULP chip designs. If trends hold, we’ll see 1 trillion transistors in a chip package by the end of the decade.

CXL-Attached Memory Gets Real

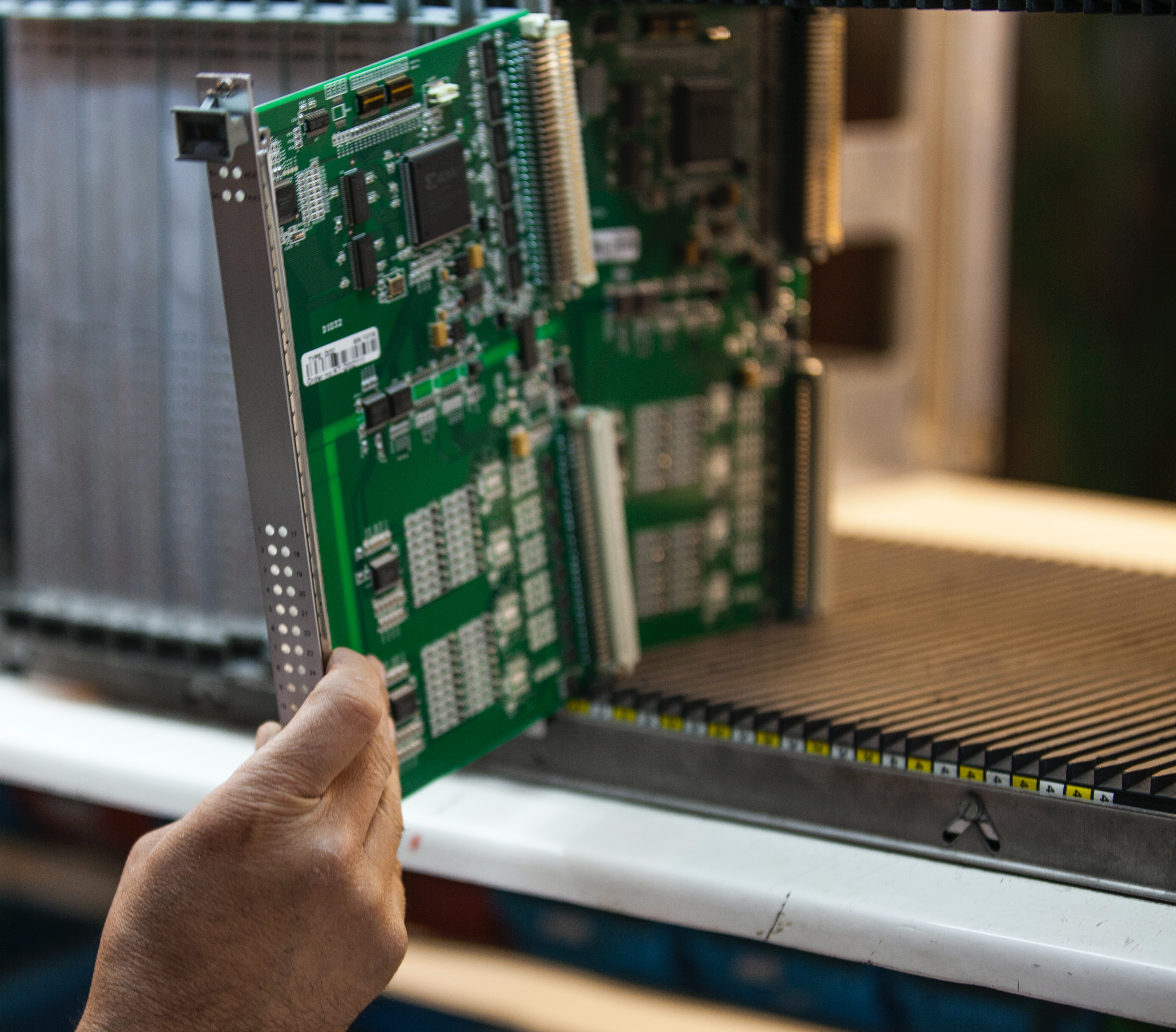

Computer Express Link (CXL) memory is the market’s solution to the insatiable demand for more memory brought on by cloud computing and big data. Built on top of the latest PCI Express standard for peripherals, CXL memory can connect processors of any type and memory into a single memory space.

Cloud computing is already hurtling in this hyperscaling direction, and large embedded systems will enjoy many of the same benefits. Systems using CXL are able to create memory partitions, compute, and offer connectivity from within the same common pool of resources. CXL-attached memory controllers equip center operators with the valuable ability to customize systems so that memory errors, material degradation, environmental impacts, and manufacturing defects are not crippling — the rest of the system is flexible enough to accommodate for failure.

Manufacturers like Astera Labs have already begun to deliver CXL-attached memory controllers for high volume deployment, providing server-grade Reliability, Availability, and Serviceability (RAS) in an efficient and resilient technology.

Ultra-Low-Power Chips Expedite Energy-Efficient Designs

Flexibility isn’t the only priority of modern systems. Many of the latest electronic products depend upon the stingiest possible use of power — and the impressive battery life that comes with it — for market success. Manufacturers of products ranging from medical devices to wearables, industrial systems, and IoT appliances are all clamoring for more access to super-efficient MCUs. Ultra-Low-Power (ULP) devices already made up 32% of all microcontrollers shipped in 2020. By 2027, that share is projected to surpass 70%.

This proliferation of ULP MCUs is a direct result of the continuous shrinking of process nodes. Miniaturized dies drastically improve power efficiency by boosting logic, SRAM, and analog densities — among other performance enhancements — all with the same level of power consumption. In many cases, the ULP device even realizes a net reduction in power.

Such gains are necessary to meet the design goals of today’s cutting-edge technologies, such as patient wearables in healthcare. These devices must read, monitor, and process data sets continuously while also transmitting information to the cloud. Such functions require numerous additional components that must also fit inside the device. As wearables, which already need to be lightweight and long-lasting, low power consumption and very small MCUs are a top priority.

New transistor technologies like FinFET are replacing older MOSFET designs to facilitate the ULP changeover. Whereas a MOSFET MCU might measure 100 mm2 at 45 nm, an equivalent FinFET design would shrink by an astounding 80% to only 20 mm2 at 14 nm.

The industrial market is involved in energy-efficient designs, too, and is a relative newcomer to the semiconductor market with enormous growth potential. The number of IoT devices are expected to double between 2021 and 2025 as we shuttle towards Industry 4.0.

Smart, interconnected, mobile, and wearable devices will only continue to spread and demand that MCUs evolve to meet market needs. This is no doubt an exciting time to be developing ULP products.

The Trillion Transistor Era To Kick Off By 2030

Speaking of tiny transistors, Intel CEO Pat Gelsinger has remarked that it will take more than smaller, cheaper transistors to propel Moore’s Law in the coming years.

The next era of ever-shrinking chips, says Gelsinger, will require a shift from the relentless pursuit to fit everything on a single System-on-Chip (SoC) to squeezing more tech into a System-in-Package (SiP). If trends hold, Intel expects that we’ll be able to progress from the more than 100 billion transistors that fit in a package today to 1 trillion transistors by 2030.

The trillion transistor era will be made possible by embedded multi-die interface bridges (EMIB), 3D logic-stacking technologies, and anything else that supports the combination of multiple silicon die (and transistors) into high-density chip packaging. This means that modern foundries are now tasked with producing not only wafers, but whole systems tied together with the software in 2.5D and 3D tile-based chip designs.

"If you think about it, the rack is becoming a system,” said Gelsinger. “And the system is becoming an advanced package of multiple dies and chiplets. Literally, the system is becoming the advanced packaging technology of the future.” Intel has supported this transition by driving for the adoption of the “Universal Chiplet Interconnect Express” (UCIe) interface as a new open standard for die-to-die interconnections built on top of the PCIe bus.

The emerging ecosystem around chiplets has the backing of cloud and tech leaders like Google, Meta, Microsoft, and roughly 50 companies that have all joined the UCIe Consortium to help open the door to tomorrow’s chip standards — and the trillion transistor SiP.

Stay Up-to-Date on Semiconductor News With Sensible Micro

The Sensible team always keeps an ear to the ground for valuable industry insights and electronic component news. Our robust global network often enables us to access critical insights early, even before many OEMs and manufacturers.

Stay informed with Sensible Micro and prepare for imminent shifts in the semiconductor market — or the technologies that drive it!

News Sources: